一种基于MF RC500的Mifare1卡读写器的设计与实现

文章出处:http://www.nexussmartsolutions.com 作者:微计算机信息 人气: 发表时间:2011年09月18日

1 引言

随着射频技术的推广,Mifare1卡已经广泛应用于公共交通终端、手持终端、板上单元、非接触式PC终端等各个非接触式通信场合。非接触式智能卡读写系统是射频技术中的一个重要组成部分,可完成指令分析、数据采集等诸多功能。这种射频读写系统的实现原理如下:由读写器向Mifare1卡,也就是射频卡发射特定频率的无线电磁波。当射频卡靠近读写器时,受读写器发射的电磁波激励,卡片内的LC谐振电路产生共振并且接收电磁波能量。当射频卡接收到足够的能量时,就将卡内存储的识别资料以及其他数据以无线电波的方式传输到读写器并且接受读写器对卡内数据的进一步操作。

本文提出了一种基于MF RC500的Mifare1卡读写器设计方案,该方案采用AT89S52单片机实现对MCM(Mifare Core Module)的控制。本文的设计方案具有硬件实现简单、易于软件二次开发等优点。同时,由于良好的电磁兼容性,该系统比较稳定,通信可靠性得到了保证。下面首先给出了系统的总体结构以及方案设计,然后从硬件设计及软件设计两个方面对系统进行了讨论和说明。

2系统总体结构及方案设计

基金资助:国家科技型中小企业技术创新基金(No.00C26212110519)

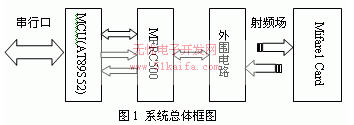

本文采用AT89S52单片机、MF RC500以及外围电路实现读写器的基本组成。读写器与Mifare1卡由射频场来建立无线链接并完成数据交换。系统总体结构如图1所示。

系统的工作方式主要是由AT89S52对MF RC500进行控制与通信,MF RC500驱动外围电路对Mifare1卡进行读写操作。具体说来,MCU(微控制器,即AT89S52)通过串行口接收PC机的指令,完成对卡的操作和整个读写器的管理;MF RC500负责信号的编码、解码,信号的调制、解调;外围电路建立读写器同射频卡之间的联系,此部分的设计直接影响到射频功率的大小以及系统的抗干扰能力;Mifare1卡是系统的应用终端,接收读写器的指令并返回指令执行结果。

3系统硬件设计

硬件主要包括微型单片机MCU、MF RC500、时钟电路、匹配电路及接口等外围电路。下面给出各部分的详细说明及相关设计。

(1) MCU部分

系统中选用低功耗、高性能的CMOS 8位单片机AT89S52。片内含8k Bytes ISP(In-system programmable)的可反复擦写1000次的Flash只读程序存储器。器件采用ATMEL公司的高密度、非易失性存储技术制造,兼容标准MCS-51指令系统及80C51引脚结构,芯片内集成了通用8位中央处理器。同时片内带有防死锁的WATCHDOG,以确保系统稳定运行。

(2) 基站部分

系统的基站单元采用PHILIPS公司生产的MF RC500芯片。MF RC500是与射频卡实现无线通信的核心部件,也是读写器操作Mifare1卡的关键接口芯片。它利用先进的调制和解调概念,完全集成了在13.56MHz下所有类型的被动非接触式通信方式和协议。MF RC500支持ISO14443A所有的层,内部的发送器部分不需要增加有源电路就能够直接驱动近操作距离的天线(可达100mm);接收器部分提供一个坚固并有效的解调和解码电路,用于ISO14443兼容的应答器信号;数字部分处理ISO14443A帧和错误检测(奇偶&CRC)。此外,它还支持快速CRYPTO1加密算法,用于验证Mifare系列产品。方便的并行接口可直接连接到任何8位微处理器,对读卡器和终端的设计提供了极大的灵活性。

MF RC500的内部EEPROM分为4部分,分别用于保存产品有关信息、存放寄存器初始化启动文件以及存放加密运算的密钥等。8×64位的FIFO用于缓存微控制器与芯片之间的输入/输出数据流,可处理数据流长度达64字节。芯片的中断请求有定时设置到、发送请求、接收请求、一个命令执行完、FIFO满、FIFO空等六种。MF RC500内有定时器,其时钟源于13.56MHz晶振信号,13.56MHz信号由晶振电路外接石英晶体产生。微处理器可借助于定时器完成有关定时任务的管理。定时器可用于定时输出计数、看门狗计数、停止监测、定时触发等工作。

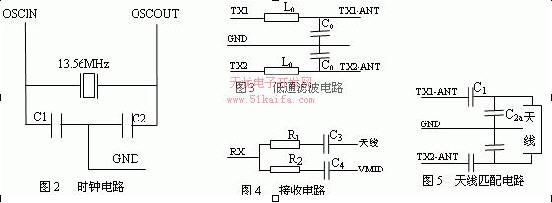

(3) 时钟电路

MF RC500内部集成了振荡器缓冲,连接外部的13.56MHz的石英震荡晶体,以获取低相位抖动,如图2所示。由于提供给MF RC500的时钟要作为同步系统的编码器和解码器的时间基准,因此频率的稳定性是正确执行的一个重要因素,为了获得最佳性能,时钟抖动应该尽可能小。

(4) 匹配电路

匹配电路包括EMC低通滤波器、接收电路、天线匹配电路和天线。

EMC低通滤波电路:MIFARE系统在13.56MHz频率下操作,石英晶振产生用于驱动MF RC500以及作为驱动天线的13.56MHz能量载波的基频,这样会产生比该频率更高的谐波,因此对输出信号必须进行适当的滤波,低通滤波器元件包括L0和C0,如图3所示。

接收电路:MF RC500的内部接收部分使用一个受益于副载波双边带的概念装入卡响应的调整,因此可以使用内部产生的VMID电势作为RX脚的输入电势。为了提供一个稳定的参考电压,必须在VMID脚接一个对地电容,如图4所示。

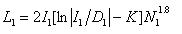

天线匹配电路:其中的元器件参数与天线的电气特性和环境有关。电路如图5所示。

天线:天线设计中,最重要的是计算出天线线圈的电感量,从而确定天线旁路电容和电阻值。一般采用经验公式对线圈电感量进行估算。假设天线设计为常用的环行或者矩形,则有:

式中, 为导体环一圈的长度;

为导体环一圈的长度; 为导线直径或者PCB板上导体的宽度;

为导线直径或者PCB板上导体的宽度;  为天线形状因素(环行天线

为天线形状因素(环行天线  =1.07,矩形天线

=1.07,矩形天线 =1.47);

=1.47);  为圈数。

为圈数。

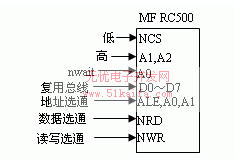

(5) MF RC500与MCU的接口电路

MF RC500支持与不同的微处理器直接接口,包括独立读写选通的MCU连接、公共读写选通的MCU连接以及具有公共读写选通和挂钩功能的MCU连接。在每次上电或硬件复位后,MF RC500也复位其并行微处理器接口模式并自动检测当前微处理器接口的类型。

本系统选用具有公共读写选通和挂钩功能的MCU连接方式,图6为MF RC500与MCU的接口原理。由图中可以看出,本系统采用中断(INT1)工作模式,即MCU利用MFRC500提供中断信息对其进行控制。另外,根据系统的需要,可以采用查询方式对MF RC500进行操作。

4系统软件设计

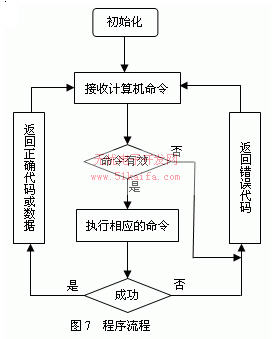

软件设计主要包括对MF RC500进行初始化、接收上位计算机的指令、控制MF RC500,并且把MF RC500的状态信息反馈给计算机。程序流程如图7所示。

(1) 初始化并行接口

首先读Command 寄存器直到Command的6位值为00H,内部初始化阶段此时结束,MF RC500准备接收控制;将80H 写入Page寄存器以初始化微处理器接口;读Command寄存器,如果该值为00H则微处理器接口初始化成功;在接口初始化之后通过将0X00 写入页寄存器,激活线性地址模式。这个过程可以用以下代码表示:

do{PReset=1; Delay(10); PReset=0;} // 给复位脉冲

while (ReadRC(RegPage) != 0x80);

do{ WriteRC(RegPage,0x0);}

while(ReadRC(RegCommand) != 0x00);

if (ReadRC(RegCommand) != 0x00)

status = MI_INTERFACEERR;//接口初始化错误

else

status = 0; //接口初始化成功

(2) 对Mifare1卡的操作

MCU对Mifare1卡操作的命令主要有空操作、装载密码、验证密码、读卡、写卡和关卡等。无论哪种操作都必须先把命令代码写入到Command寄存器,比如执行验证密码则需要执行WriteRC(RegCommand,0x0c)命令。

从操作流程上,可以把Mifare1卡的操作分为以下几项:

复位请求:当一张Mifare1卡处在读写器天线的工作范围之内时,读写器向卡发出REQUEST all(或REQUEST std)命令。卡的ATR将启动,将卡Block 0中的卡类型(TagType)号共2个字节传送给读写器,建立卡片与读写器的第一步通信联络。如果不进行复位请求操作,读写器对卡的其它操作将不会进行。

反碰撞操作:如果有多张Mifar1e卡处在读写器天线的工作范围之内时,读写器首先与每一张卡进行通信,取得每一张卡的ID号。由于每一张Mifare1卡都具有唯一的ID号,因此读写器根据卡的ID号来保证一次只对一张卡操作。

卡选择操作:完成了上述二个步骤之后,读写器必须对卡进行选择操作。执行操作后,返回卡上的SIZE字节。

认证操作:经过上述三个步骤,在确认已经选择了一张卡片时,读写器必须对卡上已经设置的密码进行认证。如果匹配,才允许进一步的读写操作。

读写操作:对卡的读、写、增值、减值、存储和传送等操作。

5结论

本文的创新工作:基于PHILIPS公司生产的MF RC500芯片,提出了一种结合单片机AT89S52的通用射频卡读写器的设计与实现方案。系统实现了对Mifare1卡读写操作的同时,具有以下优点:(1) 由于接口方式比较多,对IO口操作简单,可以方便地对MF RC500进行控制并获取相应信息;(2) 由于该系统在天线设计合理的情况下可靠性比较高,有效距离可达10cm;(3) 计算机只需通过一定的方式发送命令,即可对卡操作,在此基础上可以根据不同的需要开发出相应的九游体育·官方网站,具有很大的实用价值。

实际应用表明该读写器架构具有响应速度快、使用简单、读卡距离远和通信稳定可靠的显著优点。