浅谈SIM芯片的ESD测试与设计

文章出处:http://www.nexussmartsolutions.com 作者: 人气: 发表时间:2013年02月06日

当前,我国IC卡应用已经渗透到国民经济各行各业。各个行业的IC卡应用已陆续启动,主要涉及电信卡、社保卡、公安部身份证、卫生部健康卡、石油行业加油卡和金融业银 行卡等诸多领域。IC卡产业的发展壮大为我国的经济社会发展做出了巨大的贡献。

IC卡目前的发展趋势主要朝着高安全性和高可靠性方面发展。作为IC卡质量可靠性的重要指标之一,抗静电ESD能力是衡量IC卡产品质量的重要指标。该能力目前已作为各行业强制性检测的要求,而且抗静电的级别有越来越高的趋势,已经突破集成电路人体模式2000V的一般要求,如中国移动已要求智能卡至少要求满足4000V的检测要求。而且,ESD之后除了功能正常以外,功耗方面也要符合GSM标准的严格要求。因此,ESD设计仍然是各个SIM芯片厂商设计关注的重点,也是一款产品设计成败的关键。

上海华虹集成电路有限责任公司是国内最大的智能卡芯片开发及系统解决方案供应商,连续九年蝉联中国IC集成电路行业的前十强。本文将简要介绍SIM芯片ESD的测试现状以及主流的设计。

ESD测试模型

目前SIM产品的测试主要有三种模型:人体放电模式(HBM)、机械模式(MM)和带电器件放电模式(CDM)。人体放电模式(HBM)ESD是指因人在地面走动磨擦或其它因素在人体上累积了静电,当人碰触到IC时,人体上的静电便会经由IC的管脚而进入到IC内部,再经由IC放电到地去。该放电过程会在几百毫微秒短的时间内产生数安培的瞬间放电电流,该电流会把IC内的组件给烧毁。机器放电模式(MM)ESD是指机器本身累积了静电,当该机器碰触到IC 时,该静电便会经由IC的管脚放电。由于机器是金属材质,其等效电阻为0Ω,其等效电容为200pF。其放电的过程更短,在几毫微秒到几十毫微秒之间会有数安培的瞬间放电电流产生。带电器件放电模式(CDM)是指IC因磨擦或其它因素在IC内部累积了静电,但在静电累积的过程中IC并未受到损伤。此带有静电的IC在处理过程中,当其管脚碰触到接地面时,IC内部的静电便会经由管脚自IC内部流出来,而造成了放电的现象。

有些用户关注系统级ESD测试,系统级ESD测试与HBM、MM、CDM测试模型主要有三个方面的区别:一是使芯片与其相关的终端设备作为整体进行测试,二是在带电工作状态下进行测试,三是通过接触和非接触两种方式进行触发电压测试。

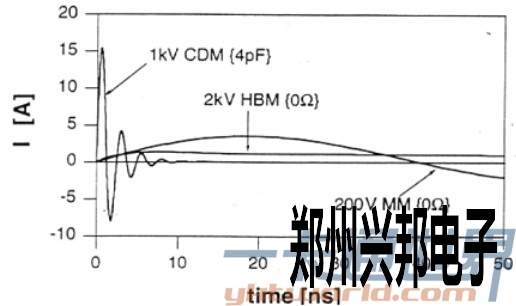

以下是2kV HBM、200V MM和1kV CDM模式的放电波形比较。虽然HBM的电压2kV比MM的电压200V大,但是200V MM的放电电流却比2kV HBM的放电电流要大很多,因此,机器放电模式对IC的破坏力更大。1kV CDM模式的电流最大,放电时间最短(图1)。

图1:HBM、MM、CDM模式波形比较。

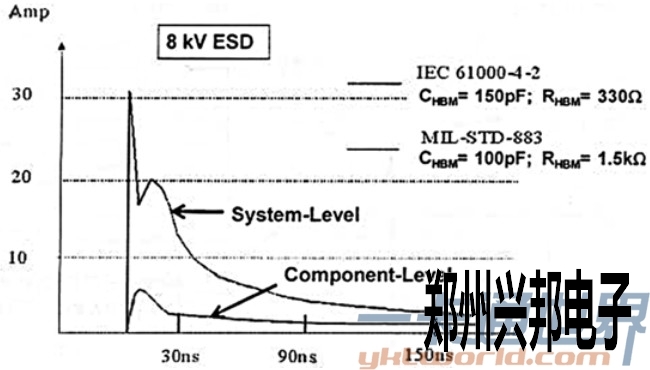

目前,ESD测试主要关注HBM模式。在电信卡第三方测试、银 行卡第三方检测机构的测试过程中,也都采用了电子qiang进行ESD测试。电子qiang的测试主要采用SCHAFFNER公司的NSG 435型号的电子qiang测试。但此设备主要用于系统级ESD测试,主流的ESD HBM在测试机构主要采用KEYTEK ZAPMASTER设备。这两者测试的波形会有不同。一般情况下,电子qiang测试的ESD的电流会更大一些,因此,这将造成两种测试结果会有所不同。有的芯片可能会出现在ZAPMASTER设备下通过8000V测试,但通不过NSG电子qiang3000V的情况。

图2是8kV系统级ESD和人体模式ESD的测试波形。系统级ESD主要遵循IEC61000标准,人体模式主要采用美军标MIL-STD883标准。

图2:系统级ESD和器件级ESD的比较。

ESD设计保护电路设计

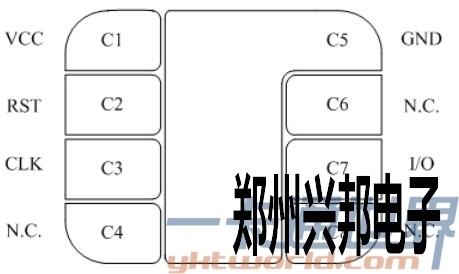

SIM芯片工艺也在不断改进。CMOS的电路尺寸不断缩小,栅氧厚度越来越薄,MOS管能承受的电流和电压越来越小,从而工艺集成度越高降低ESD性能。但是,芯片面积和价格将成为各厂商竞争的焦点,其设计一般考虑性能和面积的平衡。SIM的触点说明见图3和表1。

图3:智能卡典型封装管脚图。

表1:智能卡典型封装管脚列表。

ESD保护原理

ESD 保护电路设计的目的是提供瞬间大电流的快速泄放通路,以避免工作电路成为ESD放电通路而遭到损害。为了保证各个管脚都具有ESD保护能力,每个管脚都要设计ESD保护电路。电源脚、输入脚和输出脚因其功能不同,ESD保护电路也不尽相同。在电路正常工作时,抗静电结构是不工作的;在保护电路时,抗静电结构自身不能被损坏,并防止静电结构发生闩锁。

ESD设计架构和改进

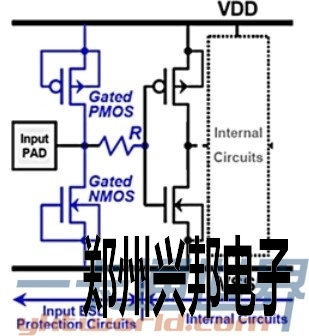

ESD保护电路主要在SIM的三个 PAD(RST、CLK、IO)内部(图4)。PAD内部的ESD通路主要由连接到电源的PMOS和连接到地的NMOS两个通道形成。二极管形成电源和地之间的保护器件。由于ESD放电的路径可能发生在任何两个PAD之间,如果PAD与电源之间正向放电,那么在PAD与电源之间以及电源与地之间的保护电路的性能对于抗ESD能力将起到决定性作用——不仅要泄放电源与地之间的ESD电流,还要在PAD之间形成ESD泄放的通路。其工作原理是:当电源对地有一负向ESD脉冲时,此二极管正向导通泄放ESD电流;当电源相对地有一正向ESD脉冲时,二极管反向工作,在击穿电压附件将电压钳制在一定的电位,并泄放过量的ESD电流。

图4:典型的ESD保护电路。

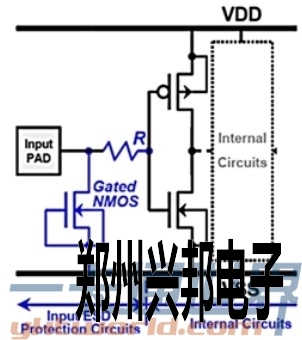

目前在市场上存在各种各样的不规范的读卡器、山寨机和终端设备,这些终端的上电时序不符合7816的规范。这可能会对这种结构的SIM芯片带来一些威胁。曾在某移动代理机构发现的一种不标准的读卡器仍然使用C6的VPP管脚。该管脚具有3.8V电压,在插入或拔卡的过程中,卡片的VCC脚会接触到激卡器的C5 脚(GND)。同时,卡片的RST会先接触到读卡器的C6脚,这样就会在VCC和RST之间瞬间形成反向电压——这个电压足以使PMOS打开并形成一个大电流,而有可能导致金丝烧断或芯片损伤。因此,对上述结构进行更改,删除PMOS与PAD之间的ESD放电通路(ESD放电NMOS是主要的ESD放电通道)(图5)。当VDD接地时,该输入PAD电压会先经过至GND的ESD防护电路,沿GND电源流向VCC与GND之间的ESD防护电路,最后经VCC 流出IC。

图5:改进后的ESD保护架构。

此外,在设计SIM ESD电路时需遵循一定的排布规则。在进行PAD排布时,各输入PAD应尽可能地并列排放,与电源和地的距离应尽可能地短,为ESD提供有效的快速放电回路。因此,在SIM外封的5个主要PAD中,RST、CLK和IO的位置应尽可能地与VCC和GND放置较近——放电路径越短,放电速度越快。电源和地的走线应尽可能宽,以减小走线的电阻。为了增加ESD的保护性能,可以建立二级ESD保护电路,保护输入、输出信号;可以在电源和地间加Power Clamp(ESD放电通道),增强电源和地间的泄防能力。

最后,提醒一下在ESD在版图中的设计要求。在工艺中,LDD(轻掺杂漏)技术、silicide(硅化物)技术和polycide(多硅结构)技术提高了CMOS的性能,但是降低了抵御ESD的能力。在版图设计时,对 MOS漏极进行加宽处理,其目的是增加漏极电阻,迫使ESD电流到来时可以引流到其它的ESD保护管中去,分散单个ESD管子的通过电流量以达到保护作用。同时,对于ESD管子采取添加阻挡层RPO,来阻挡部分的silicide和polycide。加大栅漏极的寄生电阻,ESD大电流通过后不会因过热而烧坏管子,从而达到保护管子的目的。

作者:金雁、提敏诚(上海华虹集成电路有限责任公司)